- 您现在的位置:买卖IC网 > Sheet目录320 > DK-DSP-3C120N (Altera)KIT DEV DSP CYCLONE III EDITION

28 nm Device Portfolio

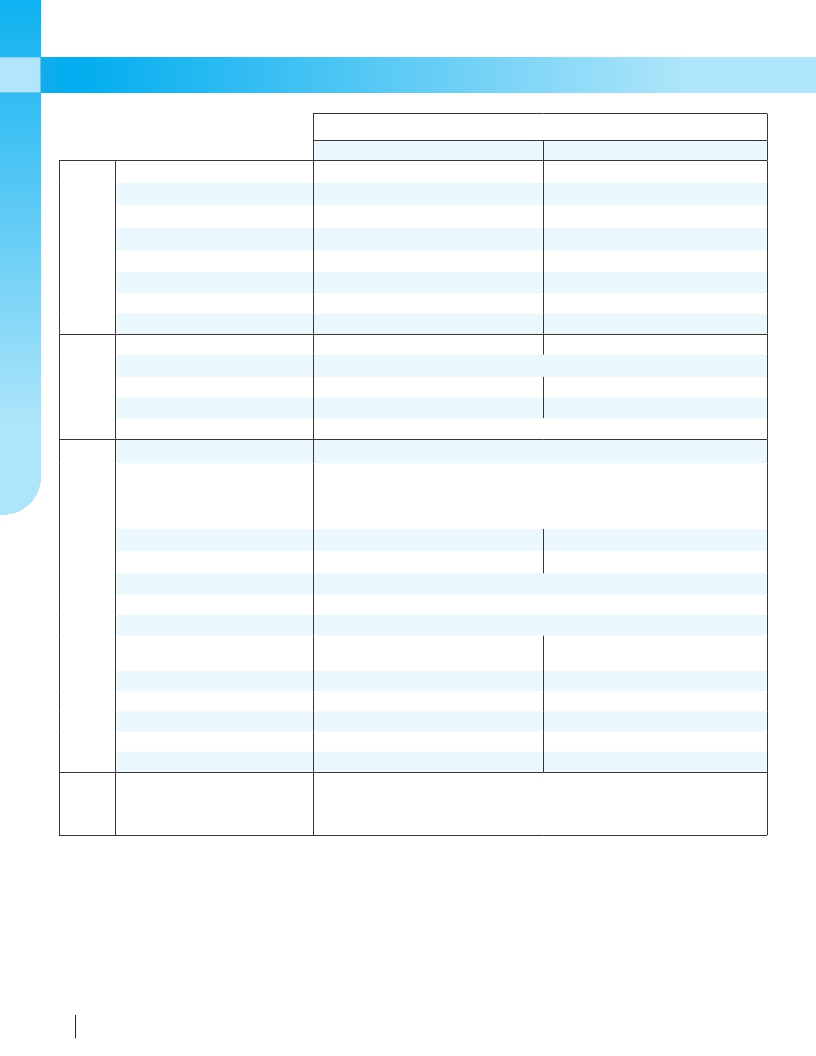

Arria V ST SoC Features

Maximum Resource Count for Arria V ST SoCs (1.1 V) 1

5ASTD3

5ASTD5

PLLs (FPGA)

PLLs (HPS)

ALMs

LEs (K)

Registers

M10K memory blocks

M10K memory (Kb)

MLAB memory (Kb)

Variable-precision DSP blocks

18 x 18 multipliers

Processor cores (ARM Cortex-A9)

Global clock networks

2

2

Design security

I/O voltage levels supported (V)

132,075

350

528,300

1,729

17,288

2,014

809

1,618

Dual

10

3

16

3

1.2, 1.5, 1.8, 2.5, 3.0, 3.3

174,340

462

697,360

2,282

22,820

2,658

1,068

2,186

Dual

14

3

LVTTL, LVCMOS, PCI, PCI-X, LVDS, mini-LVDS, RSDS, LVPECL, Differential SSTL-15,

I/O standards supported

Differential SSTL-18, Differential SSTL-2, Differential HSTL-12, Differential HSTL-15,

Differential HSTL-18, SSTL-15 (I and II), SSTL-18 (I and II), SSTL-2 (I and II),

1.2 V HSTL (I and II), 1.5 V HSTL (I and II), 1.8 V HSTL (I and II)

Hard memory controllers (HPS)

LVDStransmitter(TX)

LVDS receiver (RX)

Embedded DPA circuitry

OCT

Programmable drive strength

Transceiver count

(10.3125 Gbps/6.5536 Gbps)

PCIe hard IP blocks (Gen2 x4)

GPIOs (FPGA)

GPIOs (HPS)

Hard memory controllers 3 (FPGA)

3

136

121

16/30

2

528

216

3

1

3

Series and differential

3

136

121

16/30

2

528

216

3

1

Memory devices supported

DDR3, DDR2, DDR, QDR II, QDR II+, RLDRAM II, LPDDR2 4 , SDR

1

2

3

4

All data is correct at the time of printing, and may be subject to change without prior notice. For the latest information, please visit www.altera.com.

The PLL count includes general-purpose fractional PLLs and transceiver fractional PLLs.

With 16 and 32 bit ECC support.

These memory interfaces are not available as Altera IP.

16

Altera Product Catalog

?

2013

?

www.altera.com

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DK-K7-CONN-CES-G

KINTEX-7 FPGA CONNECTIVITY KIT

DK-K7-EMBD-CES-G-J

KINTEX-7 FPGA EMBEDDED KIT JAPAN

DK-MAXII-1270N

KIT DEV MAXII W/EPM 1270N

DK-N2EVAL-3C25N

KIT DEV NIOS II CYCLONE III ED.

DK-NIOS-2C35N

NIOS II KIT W/CYCLONE II EP2C35N

DK-NIOS-2S60N

NIOS II KIT W/STRATIX II EP2S60N

DK-PCI-2C35N

PCI KIT W/CYCLONE II EP2C35N

DK-PCIE-2SGX90N

PCIE KIT W/S II GX EP2SGX90N

相关代理商/技术参数

DK-DSP-3SL150N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3SL150F1152

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-DTK-120HW

制造商:FLORIDA MISC. 功能描述:

DKE10

制造商:MEANWELL 制造商全称:Mean Well Enterprises Co., Ltd. 功能描述:10W DC-DC Regulated Dual Output Converter

DKE10A-05

功能描述:DC/DC转换器 9-18Vin +/-5Vout 100-1000mA, 10W RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸:

DKE10A-12

功能描述:DC/DC转换器 9-18Vin +/-12Vout 42-420mA, 10W RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸:

DKE10A-15

功能描述:DC/DC转换器 9-18Vin +/-15Vout 33.3-333mA, 10W RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸:

DKE-10A-24

功能描述:DC/DC转换器 10W +/-24V 9-18VDC Dual Output DC-DC RoHS:否 制造商:Murata 产品: 输出功率: 输入电压范围:3.6 V to 5.5 V 输入电压(标称): 输出端数量:1 输出电压(通道 1):3.3 V 输出电流(通道 1):600 mA 输出电压(通道 2): 输出电流(通道 2): 安装风格:SMD/SMT 封装 / 箱体尺寸:

DKE10A-24

制造商:Mean Well 功能描述:DKE10 Series 10 W Dual Output 24 V / -24 V DC/DC Converter Power Supply 制造商:Mean Well 功能描述:Module DC-DC 2 Output 24 Volt-24 Volt 0.21A/-0.21A 10W 5-Pin 制造商:Mean Well 功能描述:Module DC-DC 2-OUT 24V/-24V 0.21A/-0.21A 10W 5-Pin 制造商:Mean Well 功能描述:D/D Module,DC/DC,Module Type,